## **Benefits of Stacked-Wafer Capacitors for High-Frequency Buck Converters**

Michael W. Baker, PhD

Maxim Integrated

Power SoC Northeastern University, Boston MA. October 7, 2014

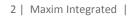

### **Mobile Device Trends**

- Power Management occupies 30% of a typical 3<sup>rd</sup>-Generation Smartphone

- Many power supplies required today:

- > Battery charger

- > Fuel gauge

- > Touch interface

- > Backlight power

- More will be required in the future:

- > Higher number of cores

- > More discrete sensor modules and functionality

- > Diverse radios and modes

- > Wearable and medical technologies

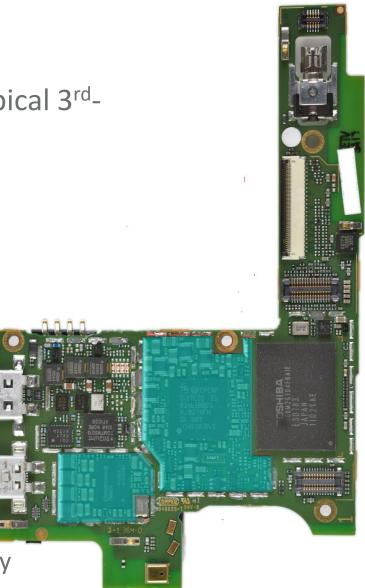

### **Mobile Power Conversion PCB Area:**

- → Many rails are required to provide optimal power for each load.

- → Majority of the area is occupied by passive components which don't shrink with Silicon process node.

- → Typically we would shrink passive components by increasing switching frequency, but resulting efficiency penalty is unacceptable.

**5-port Battery Charger**

Low Noise PA Buck

Flash Memory Buck

5-10A CPU Buck

**Backlight Power**

integrated

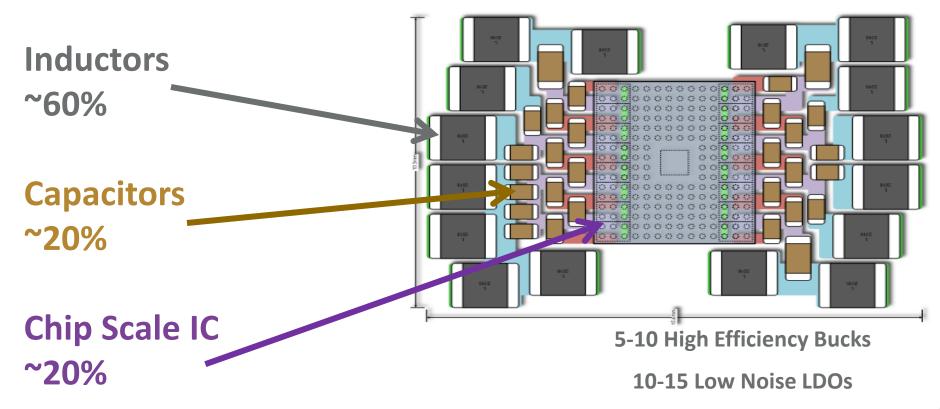

## **Optimized Buck Converter Losses**

## Power Loss Contributors Growing with Frequency:

- Turn-On and Turn-Off

Commutation "Overlap"

- Reverse Recovery

- Body Diode Conduction

- Gate charge CV<sup>2</sup>

→ Focus on reducing interconnect parasitics to enable higher frequency operation while minimizing efficiency penalties.

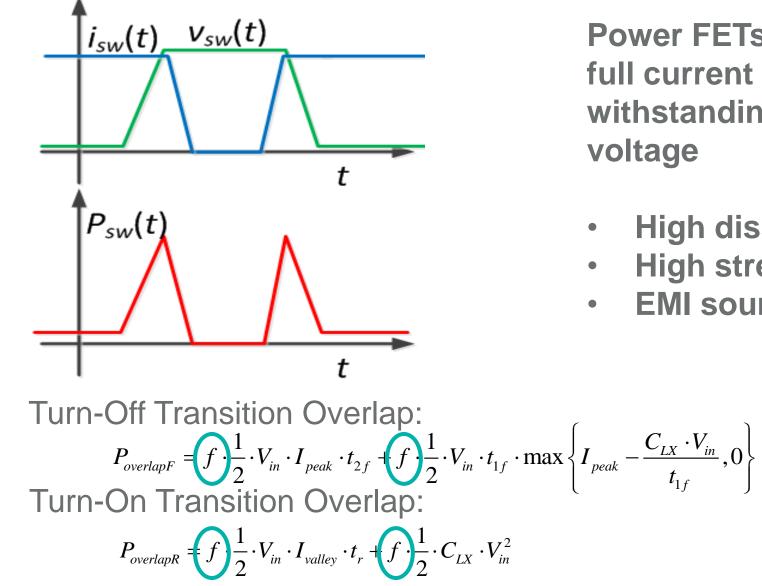

## **Turn-On and Turn-Off Commutation "Overlap"**

**Power FETs carry** full current while withstanding full voltage

- **High dissipation**

- **High stress**

- **EMI** source

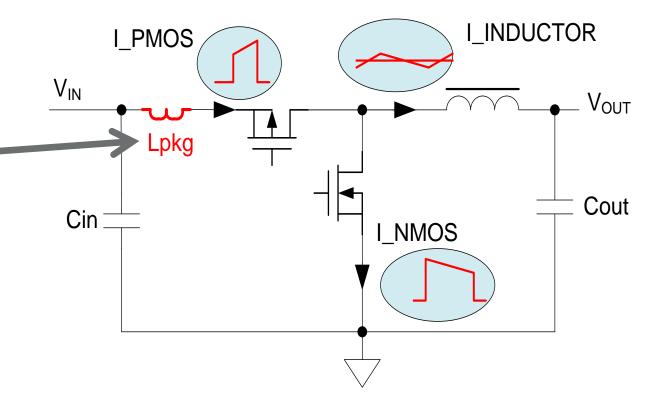

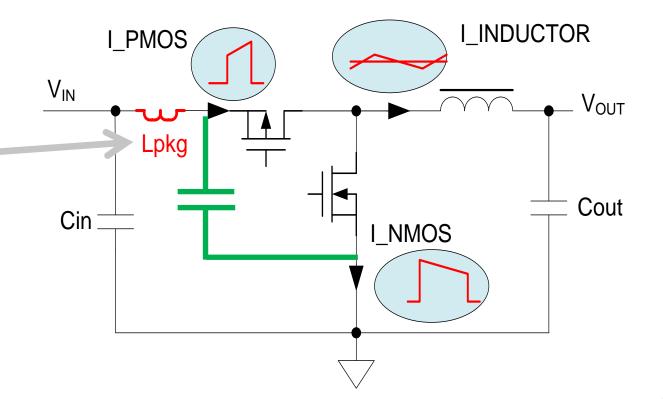

#### **Buck Converter – Input Loop Parasitic Inductance**

Fast edge rates of input current passing through package – inductance lead to ringing, EMI, and additional FET voltage stress.

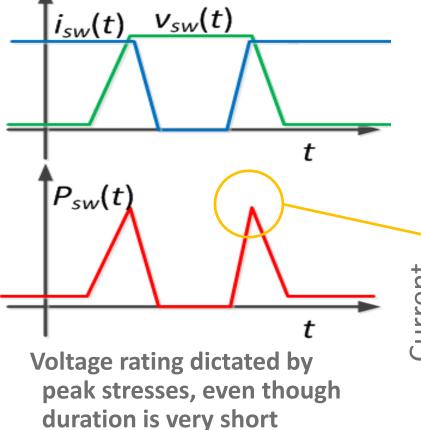

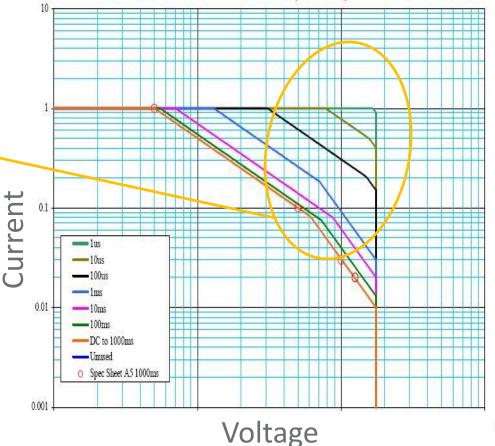

## Turn-On and Turn-Off Commutation – Safe Operating Area

Typical SOA Family of Curves for a Power MOSFET

In practice, required design margin is 30-50%

## Turn-On and Turn-Off Commutation – Integrated Capacitor

Fast edge rates of input current passing through package – inductance lead to ringing, EMI, and additional FET voltage stress.

# On-chip Cin can reduce parasitic inductance and SOA stress, allow faster commutation, increase efficiency.

## **On-Chip Input Capacitor - Candidates**

| Capacitor Type             | Structure                                    | Density at 5V (90nm)                                           | Parasitic ESL |

|----------------------------|----------------------------------------------|----------------------------------------------------------------|---------------|

| MOM CAP                    | Metal fringing capacitance                   | 0.1-0.2 fF / μm²                                               | < 100pH       |

| MOS CAP                    | MOSFET Gate Oxide                            | 1-2 fF / μm²                                                   | < 100pH       |

| MIM CAP                    | Dedicated metal-<br>insulator-metal sandwich | 1-2 fF / μm²                                                   | < 100pH       |

| Full Stack                 | MOS + MIM + 4 x MOM                          | 2.5 - 5 fF / μm²                                               | < 100pH       |

| Discrete Chip<br>Capacitor | eMGA package, low<br>profile                 | 0.5uF 0402 = 1μF / mm <sup>2</sup><br>1000fF / μm <sup>2</sup> | ~500pH        |

| Discrete Chip<br>Capacitor | On PCB, 1mm height                           | 1uF 0402 = 2μF / mm <sup>2</sup><br>2000fF / μm <sup>2</sup>   | ~1-2nH        |

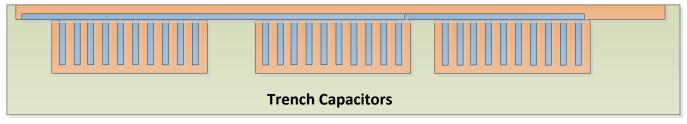

### **Trench Capacitor Technology**

Not to scale

Wafer-scale Silicon Trench Capacitor Technology: 600 fF/μm<sup>2</sup> @ 5.5 MOV, TDDB 10 year; V<sub>BD</sub> 19V, 1000fF/μm<sup>2</sup> @ 3.3 MOV, TDDB 10 year; V<sub>BD</sub> 11V,

Arkadii V. Samoilov, et. al, "3D Heterogeneous Integration for Analog", IEEE. 2013.

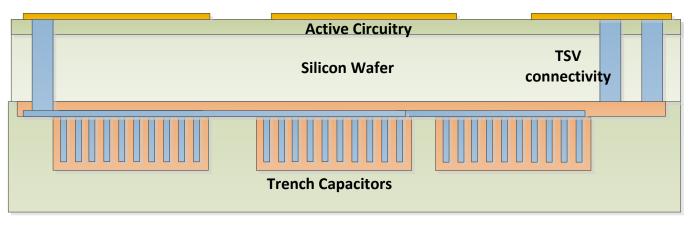

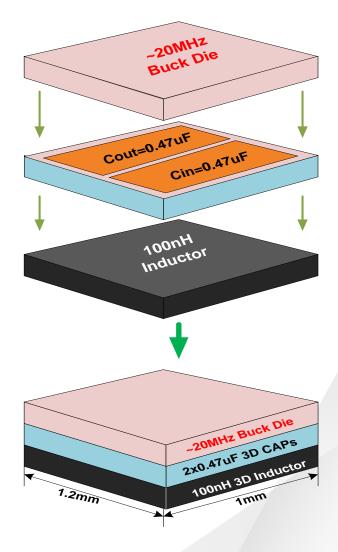

### **Wafer-scale Integration**

Not to scale

- Wafer-wafer bonding + TSV connectivity between die

- Reduces interconnect inductance by up to 10x compared to traditional PCB.

## **On-Chip Input Capacitor - Candidates**

| Capacitor Type                              | Structure                                    | Density at 5V (90nm)                                        | Parasitic ESL |

|---------------------------------------------|----------------------------------------------|-------------------------------------------------------------|---------------|

| MOM CAP                                     | Metal fringing capacitance                   | 0.1-0.2 fF / um <sup>2</sup>                                | < 100pH       |

| MOS CAP                                     | MOSFET Gate Oxide                            | 1-2 fF / um <sup>2</sup>                                    | < 100pH       |

| MIM CAP                                     | Dedicated metal-<br>insulator-metal sandwich | 1-2 fF / um <sup>2</sup>                                    | < 100pH       |

| Full Stack                                  | MOS + MIM + 4 x MOM                          | 2.5 - 5 fF / um <sup>2</sup>                                | < 100pH       |

| Trench capacitor<br>with TSV<br>integration | Deep Reactive-Ion Etched                     | 600fF / um <sup>2</sup>                                     | ~100pH        |

| Discrete Chip<br>Capacitor                  | eMGA package, low profile                    | 0.5uF 0402 = 1uF/mm <sup>2</sup><br>1000 fF/um <sup>2</sup> | ~500pH        |

| Discrete Chip<br>Capacitor                  | On PCB, 1mm height                           | 1uF 0402 = 2uF / mm <sup>2</sup><br>2000 fF/um <sup>2</sup> | ~1-2nH        |

#### **Integrated Capacitor Benefits #1: Higher Input Voltage**

# Maximum operating voltage for various input bypass capacitor configurations

| External C | Internal C | Max V <sub>IN</sub> |                                                   |

|------------|------------|---------------------|---------------------------------------------------|

| 1uF        | OuF        | 6.6V                | Nominal Design – external C <sub>IN</sub> .       |

| 22uF       | OuF        | 6.7V                | Increasing C <sub>IN</sub> does not help!         |

| 0.5 uF     | 0.5 uF     | 7.6V                | After moving half of the C <sub>IN</sub> inside.  |

| OuF        | 0.5uF      | 7.4V                | Less C <sub>IN</sub> is required when integrated. |

20% Increase in voltage headroom can enable device FOM improvement by 40%.

### **Integrated Capacitor Benefit #2: Higher Output Current**

# Maximum output current for various input bypass capacitor configurations

| External C | Internal C | Max I <sub>out</sub> |                                                                                   |

|------------|------------|----------------------|-----------------------------------------------------------------------------------|

| 1uF        | OuF        | 350mA                | Nominal Design – external C <sub>IN</sub> .                                       |

| 0.5 uF     | 0.5 uF     | 550mA                | After moving half of the C <sub>IN</sub> inside.                                  |

| OuF        | 1.0uF      | 900mA                | More <i>I<sub>out</sub></i> is possible when <i>C<sub>IN</sub></i> is integrated. |

## Integrated Capacitor Benefit #3: Lower EMI

# Conducted EMI performance for various input bypass capacitor configurations

| External C | Internal C | EMI at<br>4*Fsw | EMI at<br>8*Fsw | Relative<br>P <sub>TOTAL</sub><br>(BW=500MHz) |                                                   |

|------------|------------|-----------------|-----------------|-----------------------------------------------|---------------------------------------------------|

| 1 uF       | 0 uF       | 4.8 mV          | 2.7 mV          | 1                                             | Nominal Design – external C <sub>IN</sub> .       |

| 0.5 uF     | 0.5 uF     | 1.6 mV          | 0.8 mV          | 0.12                                          | Lowest EMI by partitioning C <sub>IN</sub> .      |

| 0 uF       | 1.0 uF     | 2.9 mV          | 1.3 mV          | 0.43                                          | Moving <i>C<sub>IN</sub></i> inside improves EMI. |

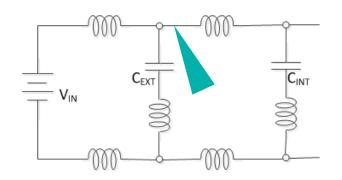

Partitioning C<sub>IN</sub> creates a higherorder Pi-network effect – 4<sup>th</sup> order roll-off.

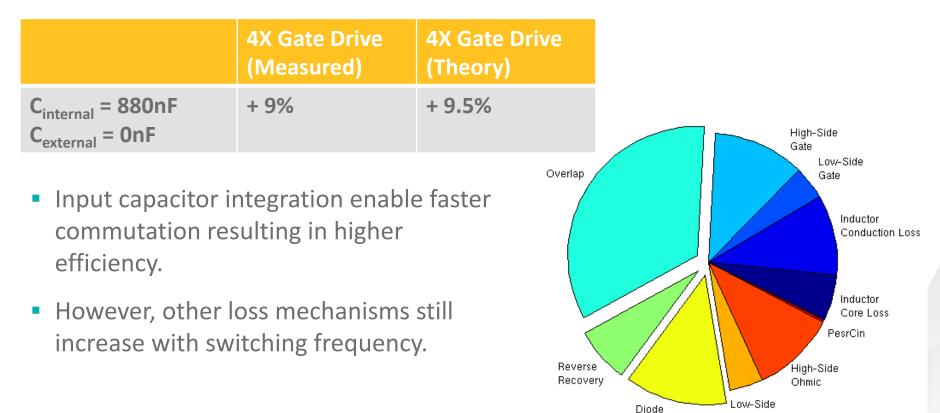

### **Integrated Capacitor Benefit #4: Minimal Frequency Impact (!)**

# Switching frequency increase enabled by integrated $C_{IN}$ , for constant efficiency.

Ohmic

ntegrated ...

Conduction

### Summary

- Integrated capacitors can improve DC-DC converter performance:

- > 20% higher input voltage capability

- > Increased output current capability (lower supply noise)

- > Reduced conducted EMI

- Demonstrated a low-ESL, high-density capacitor technology.

- Next Steps:

- > Address additional switching losses with new topologies and control.

- > Integrated inductors...

## Acknowledgements

**Colleagues at Maxim**

- Khanh Tran

- Larry Wang

- Cory Arnold

- Arkadii Samoilov

- Brett Miwa

- Joseph Ellul

## **Thank You!**